Xoilac TV xem TTBD tructiepbongda miễn phí tại Xôi Lạc TV

Xoilac trên thị trường được biết đến là địa chỉ phát sóng bóng đá hôm nay trực tiếp với đội ngũ bình luận viên hài hước, chuyên nghiệp. Thế nên, trong cộng đồng yêu thích bóng đá ở Việt Nam hiện nay, Xoi lac TV đã và đang ngày càng trở nên phổ biến. Để hiểu hơn về trang, bạn hãy tham khảo những chia sẻ tại bài viết bên dưới nhé!

Lịch sử hình thành và mục tiêu của kênh Xoi lac TV

Xoilac là kênh trực tiếp bóng đá được ra đời vào ngày 19/11/2011 khi đội ngũ Founder nhận thấy được nhu cầu của người hâm mộ trong việc xem trực tiếp các trận đấu bóng đá quốc tế. Đây là điều mà những nhà đài Việt Nam chưa thể đáp ứng được do vấn đề bản quyền.

Kênh ban đầu được thành lập với mục đích là mang đến cho người hâm mộ địa chỉ xem trực tuyến bóng đá miễn phí với chất lượng tốt nhất. Và với sự nỗ lực không ngừng từ phía đội ngũ phát triển, Xoilac đến nay đã mang đến cho người dùng rất nhiều tính năng hữu ích.

Với sự lớn mạnh về tiềm lực phát triển, Xoilac TV tính đến nay đã có sự chuyên nghiệp hơn trong phong cách hoạt động. Đồng thời mở rộng quy mô hoạt động để có thể đáp ứng được tối đa mọi nhu cầu của người hâm mộ với môn thể thao vua.

Xem truc tiep bong da Xoilac TV có gì hấp dẫn mà nhiều người truy cập đến thế?

Xoi lac TV ngay từ những ngày đầu ra mắt đã luôn thu hút số lượng lớn người hâm mộ môn thể thao vua trên toàn thế giới nói chung và Việt Nam nói riêng. Bởi kênh đã và đang tạo nên những giá trị lợi ích vô cùng thiết thực như:

Quy tụ các giải đấu bóng đá lớn nhỏ

Xoilac là địa chỉ phát sóng đầy đủ và đa dạng mọi giải đấu bóng đá. Đến với chúng tôi, những người có niềm đam mê với môn thể thao vua sẽ được theo dõi tùy ý bất cứ một trận đấu bóng đá nào dù là giải đấu trong lẫn nước ngoài như:

- Premier League

- UEFA Champions League

- La Liga

- Serie A

- Bundesliga

- V League

- World Cup

- UEFA Euro

- Copa America

- …

Đội ngũ bình luận viên chuyên nghiệp

Anh em khi đến với kênh thì chắc chắn sẽ có được những màn bình luận khó quên, độc lạ và hài hước ở mỗi trận đấu. Bởi chúng tôi hiện nay đang sở hữu lực lượng bình luận viên nắm vững kiến thức chuyên môn, số lượng đông đảo, hiểu rõ luật cũng như các vấn đề liên quan đến môn thể thao vua.

Hơn nữa, một điểm đặc biệt giúp Xoilac tạo nên thương hiệu chính là sự dí dỏm, hài hước của các bình luận viên trong quá trình bình luận. Đặc biệt, tất cả MC, bình luận viên của kênh còn tường thuật trận đấu bằng tiếng Việt 100%.

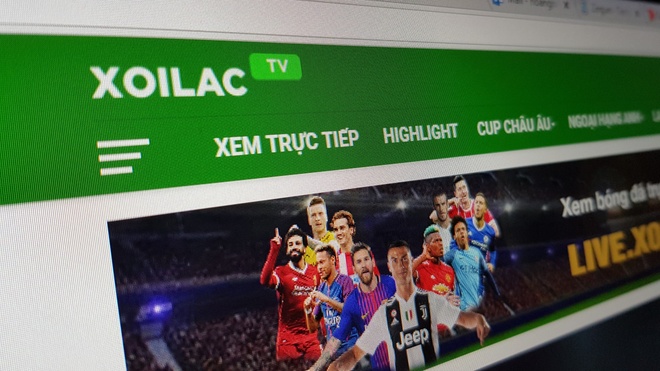

Thiết kế giao diện bắt mắt, ấn tượng

Giao diện website có thiết kế thân thiện với người dùng và vô cùng bắt mắt. Bởi chúng tôi đã có sự khảo sát và nghiên cứu vô cùng kỹ lưỡng thông qua sở thích, thói quen của người dùng. Nhờ vậy, giao diện không chỉ vừa thông minh, quen thuộc mà còn đảm bảo mang đến nhiều lợi ích nhất khi truy cập.

Đặc biệt, website còn có thiết kế màu sắc vô cùng hài hòa nên không khiến cho người chơi dù sử dụng lâu cũng không khó chịu. Đi kèm còn là một bố cục hết sức rõ ràng, khoa học nên người dùng sẽ nhanh chóng tìm kiếm được tính năng bản thân muốn sử dụng chỉ sau một lần nhấp chuột.

Link trực tiếp bóng đá tại Xoilac chất lượng cao

Chất lượng phát sóng các trận đấu chính là một trong những ưu điểm lớn nhất của Xôi lạc tính cho đến hiện tại. Cụ thể, khi tham gia theo dõi các trận đấu, bạn sẽ được tận hưởng những video phát sóng với chất lượng sắc nét, full HD, sống động về âm thanh.

Hơn nữa, chúng tôi còn luôn cập đến đến người xem đầy đủ mọi link xem bóng đá từ khá sớm. Đặc biệt, đi kèm với mỗi trận còn là 3 đường link dự phòng để anh em tùy ý chọn lựa. Xoilac cam kết tất cả link đều đảm bảo chất lượng, ko chứa mã độc hay virus khiến cho thiết bị của người dùng gặp sự cố.

Chất lượng video từ HD trở lên, giúp cho hình ảnh rõ nét

Mỗi video phát sóng bóng đá trực tiếp tại Xôi lạc TV đều được cam kết đảm bảo chất lượng tốt nhất. Hình ảnh chúng tôi cung cấp đều từ HD trở lên nên đảm bảo cho người dùng sự sắc nét, rõ ràng và đặc biệt là không khiến cho mắt bị nhức mỏi, khó chịu hay gây ảnh hưởng nghiêm trọng dù là theo dõi trong thời gian dài.

Âm thanh hiện trường tại sân vận động rõ ràng

Đi kèm với hình ảnh thì chắc chắn phải là hệ thống âm thanh sống động, đẳng cấp. Bởi chúng tôi luôn chú trọng vào trải nghiệm cũng như cảm xúc của người hâm mộ. Thế nên, âm thanh của mỗi trận đấu bóng đá được phát sóng trực tiếp đều là tiếng thu một cách rõ ràng tại hiện trường sân vận động. Qua đó, người hâm mộ sẽ có cảm giác chân thực nhất.

Nói không với các banner và clip quảng cáo xuất hiện trong video trực tiếp bóng đá

Trong quá trình hoạt động, chúng tôi luôn đề cao tính trải nghiệm của mọi người dùng. Thế nên, lựa chọn Xôi lạc TV để theo dõi các trận đấu bóng đá, bạn sẽ hoàn toàn không gặp tình trạng quảng cáo xuất hiện. Hơn nữa, các banner quảng cáo tại giao diện trang chủ cũng được chúng tôi sắp xếp rất gọn gàng, khoa học với kích thước nhỏ để không khiến nội dung trang bị che khuất.

Cập nhật tin HOT về làng túc cầu đầy đủ

Ngoài phát sóng bóng đá trực tiếp, Xoilac TV còn cung cấp đến người hâm mộ đầy đủ mọi tin tức HOT về làng túc cầu trên thế giới nói chung. Đó bao gồm những thông tin sân cỏ lẫn bên lề sân cỏ. Tất cả còn được đảm bảo tổng hợp nhanh chóng, kịp thời từ các nguồn uy tín. Thế nên, khi truy cập trang mỗi ngày, anh em sẽ cập nhật được cho bản thân nhiều kiến thức hữu ích liên quan đến môn thể thao vua.

Xôilac TV có hệ thống bảo mật chắc chắn

Đến với Xôi lạc, anh em sẽ có thể hoàn toàn yên tâm về vấn đề bảo mật. Bởi chúng tôi luôn cam kết bảo vệ tối ưu nhất về thông tin của người dùng theo đúng các điều khoản tại chính sách bảo mật. Hơn nữa, kênh còn ứng dụng công nghệ mã hóa, lưu trữ thông tin tối tân nhất thị trường. Thế nên, đảm bảo không một bên thức 3 nào có thể đánh cắp được thông tin của khách hàng khi chưa được chính chủ cho phép.

Cung cấp những tính năng quan trọng trên trang chủ

Với thiết kế khoa học, thông minh về bố cục trang nên khi đến với Xoilac TV, anh em hoàn toàn không gặp bất cứ vấn đề gì khó khăn trong việc tìm kiếm các nội dung bản thân mong muốn. Bởi tại giao diện trang chủ, chúng tôi đã phân chia các danh mục cung cấp một cách rõ ràng, dễ nhìn và dễ thao tác nhất. Qua đó, anh em dù là lần đầu tiên ghé qua cũng nhanh chóng tìm thấy hạng mục bản thân cần.

Xoilac tv trực tiếp bóng đá có link xem bóng đá chính xác

Khi xem bóng đá trực tuyến, một trong những vấn đề mà nhiều người dùng gặp phải nhất chính là link hỏng, link lỗi, link không chính xác. Thấu hiểu được vấn đề này, Xoilac đã xây dựng hệ thống link chính cũng như link dự phòng đảm bảo chất lượng để cung cấp cho người dùng.

Cụ thể, ở mỗi trận đấu, chúng tôi đều cung cấp đầy đủ 3 link để đảm bảo sự mượt mà nhất cho người dùng khi theo dõi. Hơn nữa, Xoilac còn xây dựng hệ thống link xem bóng đá vô cùng khủng để người hâm mộ có thể thưởng thức đầy đủ mọi trận cầu đỉnh cao.

Xoilac TV có điểm gì nổi bật so với các kênh ttbd khác?

Xoilac hiện nay có thể khẳng định là một trong những kênh phát sóng bóng đá trực tiếp đứng hàng đầu thị trường hiện nay. Đặc biệt, so với những địa chỉ khác, chúng tôi có sự đa dạng hơn về số lượng bình luận viên cũng như đảm bảo về chất lượng trận đấu. Chính điều này đã góp phần không nhỏ giúp kênh ngày càng có sự thu hút lượng người theo dõi đông đảo hơn.

Ngoài ra, chất lượng bình luận viên của Xoilac còn được nhận định là vui vẻ, nhiệt tình hơn. Thế nên, khi theo dõi trận đấu, người hâm mộ sẽ luôn cảm nhận được sự cuốn hút và đỉnh cao hơn ở mỗi trận đấu.

Xem trực tiếp bóng đá Xoilac TV bị giật lag phải làm sao?

Tình trạng lag, giật là một trong những vấn đề chung mà tất cả mọi kênh phát sóng bóng đá trực tiếp hiện nay đều gặp phải và Xoilac cũng không ngoại lệ. Thế nên, để đảm bảo quá trình theo dõi trận đấu không bị diss ra, lag, giật hay gặp những sự cố gây gián đoạn thì bạn hãy đảm bảo đường truyền mạng ổn định và cầu hình thiết bị xem đủ mạnh.

Ngoài ra, nếu đang theo dõi trận đấu và gặp tình trạng bị văng ra, lag hay giật thì anh em hãy đổi server, link dự phòng khác để tiếp tục theo dõi trận đấu. Bên cạnh đó, trước thời điểm phát sóng trận đấu khoảng 1 giờ thì bạn hãy thử các link được hệ thống cung cấp một cách lần lượt để kiểm tra. Nếu không tìm được đường dẫn thích hợp thì anh em hãy liên hệ với bộ phận chăm sóc của chúng tôi để được hỗ trợ.

Hướng dẫn các bước xem trực tiếp bóng đá trên XoilacTV

Để theo dõi các trận đấu bóng đá trực tiếp tại Xoilac TV thì anh em chỉ cần thực hiện một số bước đơn giản đó là:

- Bước 1: Mở trình duyệt web trên thiết bị mà bạn đang sử dụng như: Google Chrome, Opera, Cốc Cốc, Firefox…

- Bước 2: Trên thanh công cụ tìm kiếm của trình duyệt web, bạn hãy điền Xoilac hoặc Xoilac TV. Sau khi hệ thống hiển thị kết quả tìm kiếm, anh em hãy chọn link chính thống của chúng tôi.

- Bước 3: Khi đã vào trang chính thống của Xoilac, anh em hãy lựa chọn danh mục mà bản thân muốn theo dõi như: Trận hot, hôm nay, đang đá… Sau đó, chọn lựa trận đấu mà bạn yêu thích.

- Bước 4: Anh em hãy click vào đường dẫn bản thân muốn xem, sau đó chọn tiếp độ phân giải cũng như điều chỉnh kích thước, âm thanh vào thưởng thức trận đấu.

Quy tắc khi xem bóng đá tại XoilacTV

Khi theo dõi các trận đấu bóng đá trực tiếp tai Xoilac TV thì anh em cần lưu ý đến một số quy tắc như:

- Để thoải mái theo dõi các trận đấu bóng đá được ổn định thì anh em cần phải kết nối nguồn mạng ổn định.

- Trong trường hợp trận đấu bị gián đoạn nhưng nguyên nhân không phải do hệ thống mạng thì bạn hãy tạm dừng lại khoảng 2 đến 3 phút sau đó mới bấm tiếp tục để xem.

- Anh em nếu không truy cập được vào link xem trực tiếp thì hãy thoát ra và sau đó thực hiện lại sau khoảng từ 1 đến 2 phút.

So sánh Xoilac với Socolive, Cakhia, TTBD và nhiều kênh khác

Có không ít kênh phát sóng trực tiếp bóng đá trên thị trường hiện nay nhưng Xoilac TV vẫn là cái tên có sự đón nhận nhiệt tình từ phía đông đảo cộng đồng. Bởi chúng tôi mang những ưu điểm lớn mà khó có địa chỉ nào có thể đảm bảo cho người hâm mộ môn thể thao vua như:

- Miễn phí toàn bộ link phát sóng bóng đá.

- Link xem bóng đá có chất lượng tốt nhất.

- Không chứa quảng cáo trong các trận đấu khi phát sóng.

- Đảm bảo cho người sử dụng sự tuyệt đối an toàn.

- …

So sánh bóng đá xôi lạc tv với kênh truyền hình K+

Tại Việt Nam, K+ chính là một trong những kênh truyền hình chuyên biệt về bóng đá. Kênh sở hữu bản quyền phát sóng những giải đấu bóng đá số 1 thế giới hiện nay như: Premier League, Champions League, La Liga, Serie A, Europa League…

Đến với K+, anh em sẽ được trải nghiệm những trận đấu bóng đá với âm thanh sắc nét, hình ảnh chất lượng cao. Tuy nhiên, khi được so sánh thì khán giả vẫn ưu tiên lựa chọn Xoilac. Bởi chúng tôi không chỉ đảm bảo chất lượng trận đấu cho người dùng mà còn miễn phí toàn bộ. Còn khi theo dõi bóng đá tại kênh truyền hình K+ thì người hâm mộ sẽ phải trả mức phí tương đối cao.

Bình luận bóng đá trực tiếp yêu thích nhất tại Xoilac TV

Xoilac TV nổi bật trên thị trường với đội ngũ bình luận viên chuyên nghiệp, giàu nghiệp vụ, dày dặn kinh nghiệm và số lượng lớn. Chính vì vậy, khi theo dõi những trận đấu bóng đá tại kênh người hâm mộ sẽ hoàn toàn có được trải nghiệm vô cùng hoàn hảo. Hiện nay, một số bình luận viên bóng đá được yêu thích nhất tại Xoilac TV có thể kể đến như: Leo, noname…

Trực tiếp bóng đá xoilac 7 là gì?

Trong quá trình phát triển của bản thân, Xoilac sau mỗi lần bị nhà mạng chặn truy cập sẽ trở lại với một tên gọi khác nhau và Xoilac 7 chính là một trong số đó. Người dùng khi truy cập vào website sẽ có thể tùy ý theo dõi đầy đủ mọi giải đấu cũng như trận đấu bóng đá hấp dẫn ở cả trong và ngoài nước.

Tại sao nhiều quán cà phê lựa chọn kênh xem bóng đá Xoilac TV để phát sóng?

Ở thời điểm hiện tại, Xoilac chính là địa chỉ hàng đầu Việt Nam về lĩnh vực phát sóng bóng đá. Trang được nhiều người dùng, đặc biệt là các quán cà phê lựa chọn nhiều bởi rất nhiều lý do. Trong đó, nổi bật có thể kể đến như:

- Xoilac phát sóng các trận đấu bóng đá miễn phí hoàn toàn nên người truy cập không phải trả bất cứ khoản phí nào.

- Toàn bộ các trận đấu thuộc khuôn khổ những giải đấu số 1 thế giới đều được Xoilac phát sóng đầy đủ như: Ngoại hạng Anh, Bundesliga, La Liga, Serie A, Euro, World Cup…

- Cung cấp đầy đủ 3 link ở mỗi trận đấu để người dùng tiện theo dõi.

Cách tìm kiếm trang bóng đá Xoilac link chuẩn trên mạng

Để tìm kiếm Xoilac trên mạng, anh em có thể sử dụng trình duyệt web trên thiết bị của bản thân, sau đó nhập “Xoilac” hoặc “Xoilac TV” trên thanh công cụ tìm kiếm. Thông thường, những kết quả thuộc top đầu sẽ là link chuẩn của chúng tôi.

Với những link truy cập chuẩn thì người dùng sẽ thấy ngay trên menu trang chủ là rất nhiều danh mục tiện ích mà Xoilac hiện nay đang cung cấp. Ngoài ra, khi sử dụng dịch vụ, bạn cũng sẽ hoàn toàn không mất bất cứ một chi phí nào.

Các kênh mà Xoilac TV đã trải qua trong quá trình phát triển

Xoilac được chính thức ra đời từ năm 2011, tính đến nay, trang đã và trải qua không ít thăng trầm trong quá trình phát triển. Và ở mỗi giai đoạn, chúng tôi cũng đã tồn tại ở nhiều tên gọi khác nhau sau khi bị nhà mạng Việt Nam chặn về vấn đề bản quyền bóng đá. Và một số những kênh mà Xoilac TV đã trải qua trong quá trình hơn 10 năm phát triển có thể kể đến như:

- Xoilac6

- Xoilac7

- Xoilac8

- Xoilac3

- Xoilactv live

- Xoilac4

- Xoilac1

- Xoilac tv

- Xoilac2

- Xoilac5

- xoilac80.tv

- …

Các giải bóng đá được XoilacTV thường xuyên phát trực tiếp

Xoilac là địa chỉ phát sóng đầy đủ và đa dạng mọi giải đấu bóng đá. Đến với chúng tôi, những người có niềm đam mê với môn thể thao vua sẽ được theo dõi tùy ý bất cứ một trận đấu bóng đá nào dù là giải đấu trong lẫn nước ngoài thường xuyên như:

- Premier League

- UEFA Champions League

- La Liga

- Serie A

- Bundesliga

- V League

- World Cup

- UEFA Euro

- Copa America

- …

Báo chí nói gì về Xôi Lạc TV – trang xem bóng đá miễn phí

Trên thị trường, Xoilac Tv ngay từ khi xuất hiện đã nhận được sự đánh giá cao từ giới chuyên môn và báo chí. Bởi kênh mang đến cho người dùng những trải nghiệm hoàn hảo nhất với môn thể thao vua. Hơn nữa, trong quá trình phát triển, Xoilac còn không ngừng hoàn thiện và nâng cao chất lượng dịch vụ giúp người dùng cảm thấy thoải mái nhất.

Khán giả nói gì về bóng đá Xoilac TV?

Người dùng sau một thời gian đồng hành cùng Xoilac TV đã và đang có sự hài lòng vô cùng. Bởi kênh không chỉ giúp người hâm mộ được thỏa mãn đam mê với bóng đá trọn vẹn mà còn hoàn toàn miễn phí.

Ngoài ra, không chỉ giúp người dùng xem trực tiếp bóng đá, khi đến với kênh, anh em còn được cập nhật đầy đủ mọi thông tin khác liên quan đến bóng đá. Thế nêm, quá trình theo dõi trận đấu sẽ trở nên dễ dàng hơn.

Các chủ đề khác tại Xôi lạc TV ngoài link xem bóng đá

Đến với Xoilac, người dùng sẽ được thỏa mãn niềm đam mê của bản thân với môn thể thao vua. Bởi chúng tôi mang đến rất nhiều tiện ích, cụ thể có thể nhắc đến như:

Xem lại bóng đá

Với những người không kịp xem trực tiếp các trận đấu khi phát sóng thì hoàn toàn có thể ghé qua Xoilac để xem lại. Tại đây, chúng tôi không chỉ cung cấp video full trận đấu mà còn có những highlight về các khoảnh khắc ấn tượng. Qua đó, anh em có thể theo dõi nhanh chóng và không mất nhiều thời gian.

Xem kết quả bóng đá hôm nay

Đến với Xoilac, anh em sẽ được cập nhật đầy đủ mọi kết quả của các trận đấu diễn ra trong vòng 24 giờ qua. Từ đó, việc nắm bắt kết quả trận đấu hay những thông tin liên quan như: Số lần thay người, số lần ném biên, số thẻ phạt, tỷ số chung cuộc, thời lượng kiểm soát bóng… được chi tiết.

Lịch trực tiếp bóng đá

Tại Xoilac, người dùng sẽ được cung cấp lịch thi đấu của các giải đấu đang diễn ra một cách đầy đủ. Tất cả đều được cập nhật theo từng ngày, từng giờ, từng giải đấu, từng khu vực như: Đội hình ra sân, sân tổ chức, thời gian trận đấu diễn ra…

Xem tỷ lệ bóng đá hôm nay

Ngoài những tiện ích trên, Xoilac cũng cung cấp đến người dùng tỷ lệ bóng đá được cập nhật từ các chuyên gia. Thế nên, đảm bảo cho anh em xác suất chính xác là vô cùng cao.

Câu hỏi thường gặp khi xem ttbd tại Xoilac TV

Tìm hiểu về Xoilac TV, người hâm mộ cũng đặt ra không ít câu hỏi, chẳng hạn như:

Xoilac có phải là nhà cái không?

Không, Xoilac chỉ là địa chỉ cung cấp các thông tin bóng đá nói chung. Tại đây, người dùng sẽ được thỏa mãn đam mê một cách trọn vẹn nhất với môn thể thao vua.

Truy cập vào Xoilac.tv có cần đăng ký tài khoản thành viên không?

Xoilac không bắt buộc người dùng phải đăng ký tài khoản thành viên mà vẫn sử dụng được những tiện ích của trang. Tuy nhiên, để quyền lợi được đảm bảo, anh em nên tạo tài khoản thành viên.

Xoilac có yêu cầu độ tuổi truy cập không?

Để truy cập và sử dụng các tiện ích tại Xoilac thì người dùng sẽ cần phải từ đủ 18 tuổi trở lên.

Người dùng vi phạm điều khoản do Xôilac.tv cung cấp có bị xử phạt không?

Có, tất cả mọi người dùng vi phạm các điều khoản và điều kiện tại Xoilac thì đều sẽ bị xử phạt theo đúng quy định đã đưa ra.

Đăng ký làm bình luận viên tại XoilacTV khó không?

Không, chỉ cần bạn có tài năng và đam mê với môn thể thao vua thì đều có thể đăng ký trở thành bình luận viên của Xoilac.

Xoilac có hỗ trợ kết quả bóng đá trực tiếp không?

Tại Xoilac, người dùng khi truy cập sẽ được hỗ trợ kết quả bóng đá trực tiếp. Đây là tính năng không phải địa chỉ nào cũng mang đến cho khách hàng.

Xem bóng đá trực tuyến K+ có mượt hơn không?

Về chất lượng video phát sóng bóng đá trực tiếp thì cả K+ và Xoilac đều được đánh giá tương đồng nhau. Tuy nhiên, vì Xoilac là kênh miễn phí nên được nhiều người dùng lựa chọn hơn.

Tổng kết

Với các tiện ích vượt trội, Xoilac tính đến nay đã trở thành địa chỉ trực tiếp bóng đá đáng tin cậy của đông đảo người dùng Việt. Chắc chắn khi đến với chúng tôi, anh em sẽ luôn có được những trải nghiệm đẳng cấp nhất cùng trái bóng tròn.